一、IC烧录的物理本质:如何用电子“雕刻”芯片记忆

1.1 存储单元的基础结构

浮栅晶体管(Floating Gate Transistor):

以Flash存储器为例,编程时向控制栅(CG)施加高压(12~20V),通过F-N隧穿效应将电子注入浮栅(数据:电子保持寿命>10年)。

擦除时施加反向电压,电子返回衬底(擦写次数决定寿命,SLC NAND可承受10万次,QLC仅1000次)。

熔丝(Fuse)与反熔丝(Anti-Fuse):

OTP(一次性编程)存储器通过熔断金属连线(电流>50mA)或击穿介质层(电压>6V)实现永久编程(误差率<0.1ppm)。

1.2 烧录过程的三阶段模型

电气参数校准:

根据芯片Datasheet设定Vpp(编程电压,±5%精度)、Tpw(脉冲宽度,精确到0.1μs)。

案例:STM32F4系列Flash要求Vpp=7V±0.2V,脉冲序列3次/单元。

数据验证机制:

CRC32校验(误码率<1e-12) + 回读比对(全地址扫描)。

行业标准:JESD22-A117规定量产烧录需通过3次全片校验。

保护位写入:

锁定加密区域(如AES-128密钥区),熔断Security Fuse防止逆向工程。

二、烧录设备的“军备竞赛”:从手动编程器到全自动分选机

2.1 设备分类与技术参数对比

设备类型 | 适用场景 | 速度(片/小时) | 精度要求 | 代表厂商 |

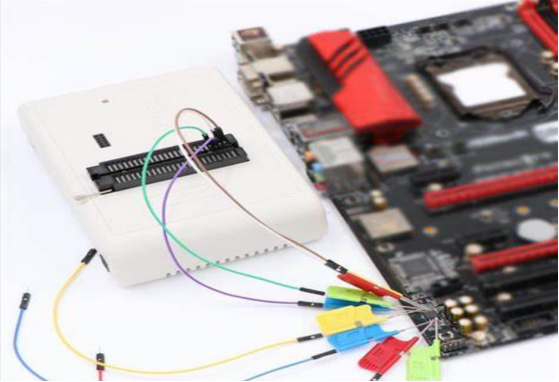

离线编程器 | 小批量研发 | 50~200 | ±5%电压控制 | Xeltek, 河洛 |

在线烧录机 | 板级烧录 | 300~500 | 同步时序<1ns | 昂科, 研华 |

分选机集成 | 晶圆/芯片级量产 | 10,000+ | 接触电阻<10mΩ | 泰瑞达, 爱德万 |

2.2 量产效率优化实战

并行烧录技术:

采用多核架构(如FPGA+ARM异构),单机支持32通道同步编程(速度提升16倍)。

限制:电源功率需满足Σ(Vpp×Ipp×通道数),例如32通道Flash烧录需500W供电。

动态功耗管理:

根据芯片状态实时调整电压(如待机时Vpp从12V降至3.3V),能耗降低40%。

三、烧录失败的七大元凶与破解之道

3.1 硬件级故障(占比68%)

触点氧化:探针接触电阻>5Ω时导致编程电压不足(解决方案:镀金探针+乙醇清洗)。

电源噪声:纹波>50mV可能引发位翻转(需增加π型滤波电路)。

3.2 数据逻辑错误(占比22%)

地址映射错位:大端序与小端序配置错误(案例:某车规MCU因字节序反导致刹车信号异常)。

固件版本混淆:建立Golden Sample数据库,每次烧录前哈希校验(SHA-256)。

四、前沿趋势:烧录技术的“静默革命”

eFuse技术:通过软件指令改写存储器配置(如高通骁龙芯片动态调整CPU频率),淘汰物理熔丝。

光子烧录:利用飞秒激光直接修改芯片金属层(精度达0.1μm),突破传统电气限制。