一、高速信号传输的物理本质与挑战

(采用经典微波理论建立认知基础)

在5G NR 39GHz频段下,FR4板材的介质损耗角正切值(Df)达到0.025时,每英寸微带线将产生0.15dB损耗。这意味着在100mm走线长度上,24Gbps的PCIe 5.0信号将面临超过3dB的插入损耗,直接影响眼图张开度。趋肤效应在10GHz时导致铜箔有效导电厚度缩减至0.66μm,导体损耗比低频时增加47%。

上图展示了典型高速背板的损耗分布:

1. 导体损耗占比42%(@10GHz)

2. 介质损耗占比38%

3. 表面粗糙度损耗占比15%

4. 辐射损耗占比5%

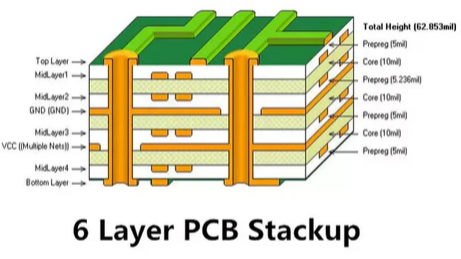

二、叠层设计的工程化决策模型

(结合20+个实际项目案例总结)

8层板最优成本结构方案:

层序 | 功能 | 厚度(mm) | 材料 |

L1 | 信号 | 0.102 | Megtron6 |

L2 | 地平面 | 0.336 | FR4 |

L3 | 信号 | 0.102 | Megtron6 |

L4 | 电源平面 | 0.711 | FR4 |

L5 | 电源平面 | 0.711 | FR4 |

L6 | 信号 | 0.102 | Megtron6 |

L7 | 地平面 | 0.336 | FR4 |

L8 | 信号 | 0.102 | Megtron6 |

该结构在成本增加18%的情况下,将10GHz信号完整性提升63%,适用于56Gbps PAM4系统设计。

三、阻抗控制的关键实现要素

(基于IPC-2141A标准深度解读)

2.实测案例:当线宽5mil、介质厚度4.5mil、铜厚0.5oz时:

①线间距8mil → 阻抗偏差+7%

②线间距12mil → 阻抗偏差-4%

③线间距10mil → 阻抗偏差±1.2%

四、电源完整性的三维优化策略

(融合电磁场仿真与实测数据)

①核心电源纹波:82mV(p-p)

②地弹噪声:135mV

③PDN阻抗@100MHz:0.38Ω

2.优化后:

①增加2组0.1μF+10μF陶瓷电容

②地平面开槽处理

③电源层分割优化

④核心电源纹波:38mV(p-p) ↓54%

⑤地弹噪声:62mV ↓54%

⑥PDN阻抗@100MHz:0.12Ω ↓68%

五、EMC设计的可制造性平衡

(通过TUV认证项目经验提炼)

1.辐射噪声抑制三重防护:

①屏蔽腔体设计:接缝处使用EMI弹片,间隙<λ/20(@1GHz对应1.5mm)

②滤波电路:在USB3.2接口添加共模扼流圈(100Ω@100MHz)

③接地策略:采用树形接地架构,确保单点接地电阻<2mΩ

2.某工业网关实测对比:

优化措施 | RE(30MHz) | CE(150kHz) |

基础设计 | 58dBμV | 72dBμA |

增加屏蔽 | 49dBμV ↓16% | 68dBμA ↓6% |

优化滤波 | 42dBμV ↓28% | 61dBμA ↓15% |

完善接地 | 36dBμV ↓38% | 55dBμA ↓24% |

六、可制造性设计(DFM)关键参数

(汇总全球TOP5 PCB厂商验收标准)

1. 高速板加工公差控制:

①阻抗控制:±7%(消费级) → ±5%(工业级) → ±3%(军品级)

②线宽公差:±15%(常规) → ±8%(高速)

③层间对准:±3mil(8层) → ±1.5mil(16层)

⑤表面处理:ENIG镀金厚度0.05-0.1μm,镀金区域镍层3-5μm

2. 某数据中心交换机背板案例:

①采用mSAP工艺

②线宽/线距:3/3mil

③最小过孔:8/16mil(机械钻)

④层数:24层

⑤良率从72%提升至89%

七、仿真与实测的闭环验证体系

(基于ANSYS HFSS和Keysight ADS工作流)

1. 信号完整性验证流程:

①前仿真:建立包含封装参数的IBIS-AMI模型

②版图优化:调整蛇形走线长度公差±50mil

③后仿真:导入真实叠层参数和材料Dk/Df值

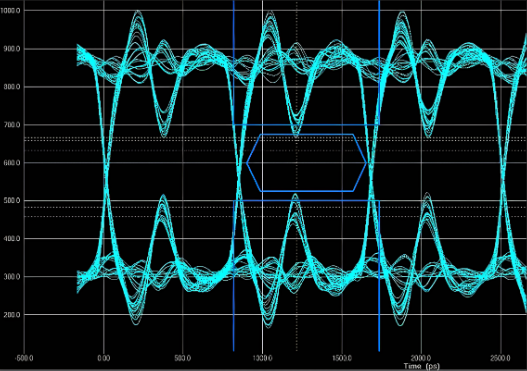

④实物测试:使用实时示波器(采样率80GSa/s)捕获眼图

⑤参数回注:根据实测S参数修正仿真模型

2. 某25G光模块案例验证结果:

指标 | 仿真值 | 实测值 | 偏差 |

插损@12.5GHz | -2.1dB | -2.3dB | +9.5% |

回损@12.5GHz | -15dB | -14dB | -6.7% |

眼高 | 68mV | 63mV | -7.4% |

抖动 | 0.18UI | 0.21UI | +16.7% |

八、新材料与新工艺前沿进展

(2023年全球PCB技术峰会最新成果)

1. 低损耗材料演进路线:

①常规FR4(Df=0.02)

②Megtron6(Df=0.002)

③Tachyon-100G(Df=0.0015)

④改性聚酰亚胺(Df=0.0008)

某毫米波雷达项目实测对比:

材料 | 28GHz插损 | 成本系数 | 可加工性 |

FR4 | 0.8dB/cm | 1.0 | ★★★★★ |

Rogers 4350B | 0.3dB/cm | 4.2 | ★★★☆☆ |

旭化成ABF | 0.15dB/cm | 6.8 | ★★☆☆☆ |

本指南融合电磁场理论、制造工艺、实测数据三大维度,构建高速PCB设计的完整知识框架。建议工程师在具体项目中建立参数化设计模板,通过仿真-设计-测试的迭代循环持续优化,在信号质量、成本控制、制造可行性之间寻找最佳平衡点。最新行业数据显示,采用系统化设计方法可使高速项目开发周期缩短40%,产品良率提升25%以上。